# **Integrated IF Transceiver for Broadband Wireless Applications**

#### **FEATURES**

- Integrated TX Chain (165–175 MHz / 330–350 MHz)

- Baseband Amplifiers

- Quadrature Modulator

- Digitally Controlled VGA

- TX Output IP3: 29.5 dBm

- TX Output Noise: -166 dBc/Hz

- Integrated RX Chain (140–165 MHz / 280–330 MHz)

- IF Amplifiers

- Analog and Digital VGA

- Quadrature Demodulator

- Baseband Filters

- ADC Buffers

- IF SAW Filter Bypass

- RX Noise Figure: 4.3 dB

- RX Input IP3: 9.5 dBm

- Integrated TX and RX Synthesizers

- Integrated Cross-Polarization Interference Cancellation (XPIC) Support

- Auxiliary RX Chain

### **APPLICATIONS**

- Wireless Microwave Backhaul

- Point-to-Point Microwave

- Broadband Wireless Applications

- WiMAX IF Transceiver

#### DESCRIPTION

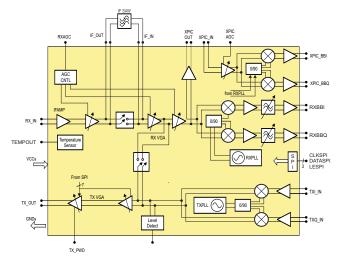

The TRF2443 is a highly integrated full-duplex intermediate frequency (IF) transceiver designed for broadband point-to-point wireless communications The receiver chain integrates applications. quadrature (IQ) demodulator and provides more than 90 dB of gain range, obtained via a combination of analog- and digital-controlled VGAs. The integrated programmable baseband low-pass filter gives the TRF2443 the flexibility to receive signals with different bandwidths, while also helping to remove interferer signals before they reach the ADC. Additionally, the TRF2443 gives the flexibility to add an external IF filter to further remove unwanted signals. The TRF2443 transmitter chain integrates a quadrature (IQ) modulator driving a highly linear IF DVGA that provides 35 dB of gain range controlled via a serial programming interface (SPI). The TRF2443 includes the two synthesizers for the receiver and transmitter chains, removing the need for external LO generation circuitry and simplifying the implementation of a frequency-division duplexing (FDD) transceiver design. The TRF2443 provides also cross-polarization interference cancellation (XPIC) support via an integrated XPIC output amplifier and receiver chain. The TRF2443 is an ideal building block for implementing the IF transceiver function in the indoor unit (IDU), which is connected via a coaxial cable interface to the outdoor unit (ODU), of a point-to-point microwave backhaul split-architecture system.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### **TRF2443 DEVICE DESCRIPTION**

Figure 1. TRF2443 Functional Block Diagram

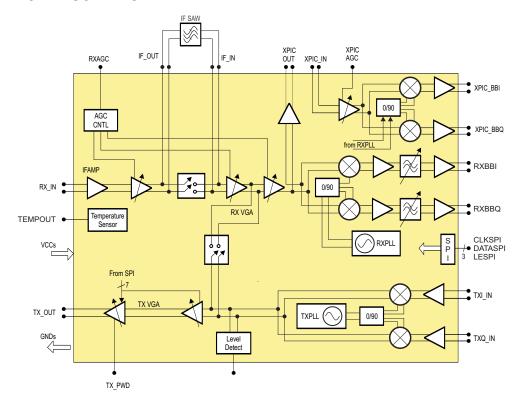

#### RECEIVER DESCRIPTION

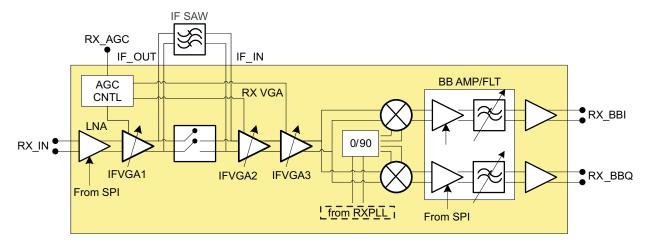

Figure 2. Receiver Chain Block Diagram

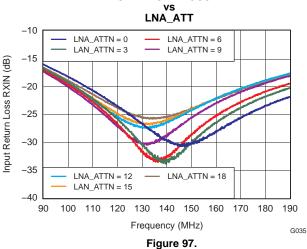

The TRF2443 features a highly linear low-noise receiver chain with over 60 dB of analog-controlled gain range and more than 40 dB of gain range programmable via the serial programming interface (SPI) in 1-dB steps. Moreover, the TRF2443 gives the flexibility to add an external IF filter to further remove unwanted signals. Such an external filter can be bypassed using an internal path that can be enabled via SPI. The first block of the

receiver chain is a low-noise, highly linear IF amplifier (LNA). Its input is differential and internally matched to 50  $\Omega$ . The TRF2443 LNA attenuation is programmable from 0 dB to -19 dB, corresponding to an LNA gain of 17 dB to -2 dB (1-dB steps). The LNA is followed by three analog-controlled VGAs that provide more than 60 dB of gain range. The IFVGA1 output and IFVGA2 input can be connected externally (pins IFOUT and IFIN) through an external IF filter. An internal switch gives the flexibility to bypass the external filter. The VGAs provide a gain slope of 51 dB/V. The IFVGA3 drives the demodulator, which downconverts the IF input signal directly to baseband in-phase and quadrature. The demodulator block includes the local oscillator in-phase and quadrature generation circuitry followed by the LO buffer. The TRF2443 baseband section integrates a programmable-gain amplifier (PGA) and programmable low-pass filter. The baseband PGA minimum gain is 9 dB, and the maximum gain is 33 dB. The TRF2443 baseband low-pass filter cutoff frequency can be programmed from 2 MHz to 11 MHz by setting the cutoff-frequency control bits appropriately. The baseband output buffers (ADC drivers) are designed to drive directly an analog-to-digital converter (ADC), either dc- or ac-coupled. The output common mode of the ADC drivers is set externally via the RXBBCM pin (pin 40). When the TRF2443 baseband output.

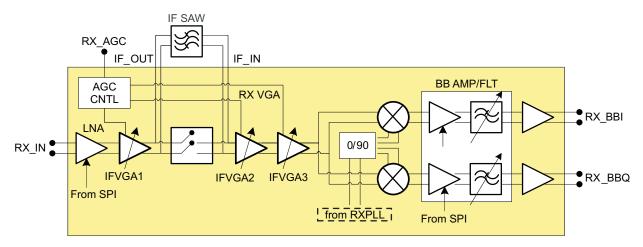

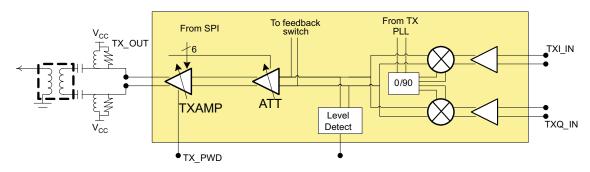

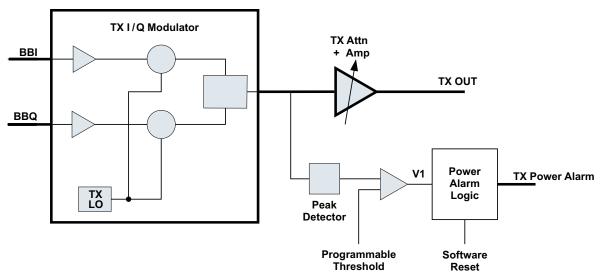

#### TRANSMITTER DESCRIPTION

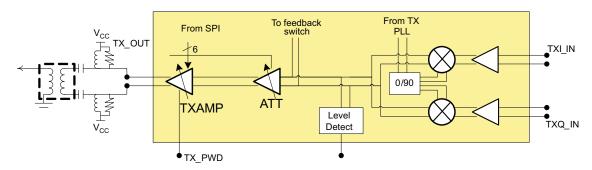

Figure 3. Transmitter Chain Block Diagram

The transmitter chain integrates an IQ modulator followed by a variable attenuator and the final transmitter amplification stage. The last two blocks provide over 35 dB of gain range. A power-alarm circuit monitors the level at the modulator output, and its digital output goes low if the signal level falls below the user-specified threshold level relative to the expected level. The first block of the transmitter chain is the IQ modulator, which upconverts the incoming in-phase and quadrature signals to the TX IF frequency. The TRF2443 can be either acord-coupled to the digital-to-analog converter (DAC). The IQ modulator drives a variable attenuator. This block provides 5.5 dB of total attenuation range in 0.5-dB steps. The output amplifier integrates five attenuator provides over 35.5 dB of monotonic output power control (0.5-dB steps).

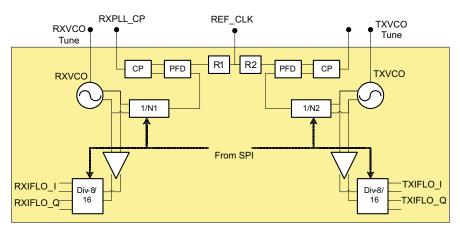

### SYNTHESIZERS DESCRIPTION

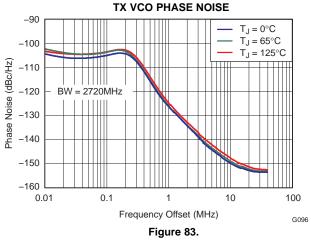

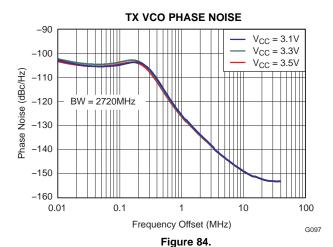

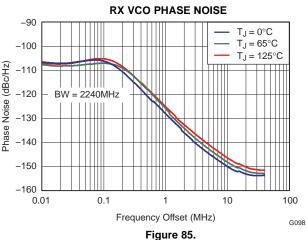

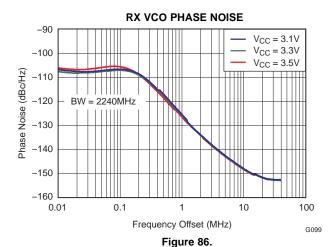

TRF2443 integrates two complete integer synthesizers for the receiver and transmitter chain. The RXVCO operates at 16 times the typical RX input frequency, and the TXVCO operates at 8 times the typical TX output frequency.

Each synthesizer is composed of:

- High-frequency VCO (around 2720 MHz for the TX VCO and 2240 MHz for the RX VCO)

- N-divider (driven by the high-frequency VCO) done by an 8/9 prescaler followed by an A-B counter that drives the phase-frequency detector

- Phase-frequency detector (PFD) (driven by the N-divider) that compares the VCO divided by N to the reference clock divided by R signals

- Charge pump (driven by the PFD) which creates up and down current pulses, based on the incoming signals from the PFD. Its output is filtered and transformed to voltage by the external loop filter and applied to the VCO input control voltage.

- An external reference clock must be applied to the REFIN (pin 16). The incoming signal is buffered and goes through a programmable divider (R-divider).

Copyright © 2009, Texas Instruments Incorporated

The VCO output is then routed through a programmable divider by 8 or 16 to create the TX and RX LO signals. The TRF2443 features a lock-detect output pin (LOCKDET, pin 5). This is a digital output that is high when both RX and TX synthesizers are locked, and it is low if one or both synthesizers are unlocked (or lose lock).

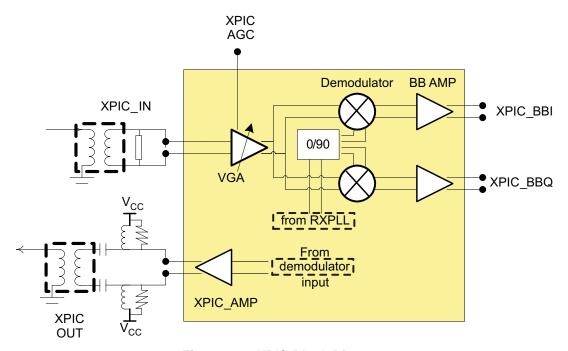

#### **XPIC DESCRIPTION**

The TRF2443 provides cross-polarization interference cancellation (XPIC) support via an integrated XPIC output amplifier and receiver chain. The XPIC output amplifier transmits the signal taken at the receiver demodulator input. The XPIC receiver section downconverts the input signal to baseband I and Q. It includes an IF VGA followed by a demodulator and a baseband amplifier.

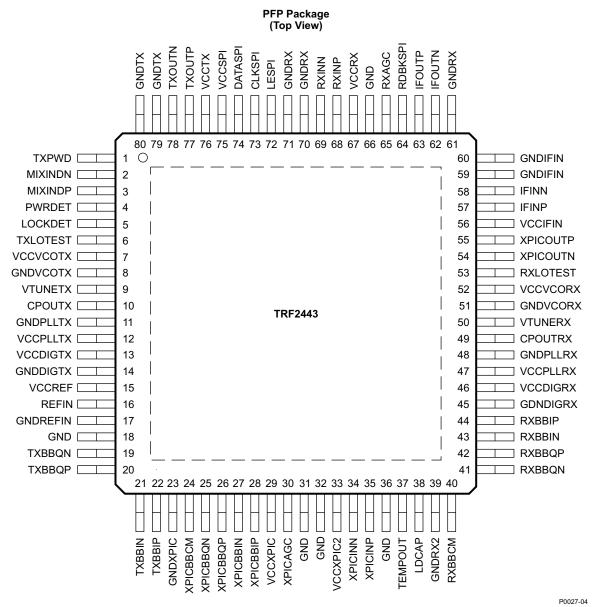

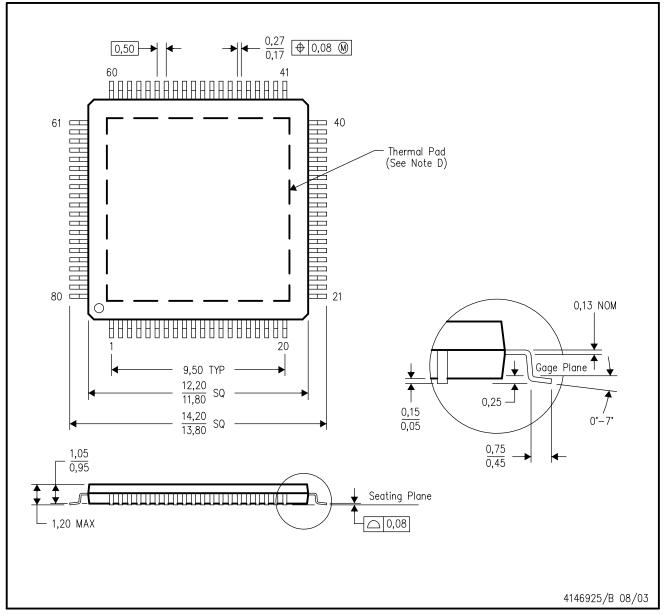

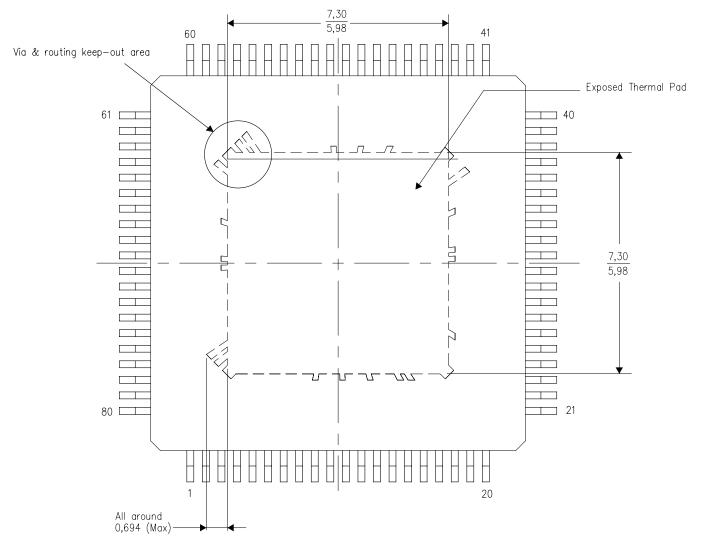

#### **PINOUT DIAGRAM**

### **PIN FUNCTIONS**

| PIN      |                          |     |                                                                                                      |

|----------|--------------------------|-----|------------------------------------------------------------------------------------------------------|

| NAME     | NO.                      | I/O | DESCRIPTION                                                                                          |

| CLKSPI   | 73                       | I   | SPI clock                                                                                            |

| CPOUTRX  | 49                       | 0   | RX PLL charge-pump output                                                                            |

| CPOUTX   | 10                       | 0   | TX PLL charge-pump output                                                                            |

| DATASPI  | 74                       | ı   | SPI data                                                                                             |

| GND      | 18, 31,<br>32, 36,<br>66 | -   | Ground                                                                                               |

| GNDDIGRX | 45                       | -   | RX PLL digital ground                                                                                |

| GNDDIGTX | 14                       | -   | TX PLL digital ground                                                                                |

| GNDIFIN  | 59, 60                   | -   | RX chain ground                                                                                      |

| GNDPLLRX | 48                       | -   | RX PLL ground                                                                                        |

| GNDPLLTX | 11                       | -   | TX PLL ground                                                                                        |

| GNDREFIN | 17                       | -   | Reference clock ground                                                                               |

| GNDRX    | 61, 70,<br>71            | _   | RX chain ground                                                                                      |

| GNDRX2   | 39                       | _   | RX chain ground                                                                                      |

| GNDTX    | 79, 80                   | _   | TX chain ground                                                                                      |

| GNDVCORX | 51                       | ı   | RX VCO ground                                                                                        |

| GNDVCOTX | 8                        | _   | TX VCO ground                                                                                        |

| GNDXPIC  | 23                       | 1   | XPIC ground                                                                                          |

| IFINN    | 58                       | I   | IFVGA2 input: negative terminal                                                                      |

| IFINP    | 57                       | I   | IFVGA2 input: positive terminal                                                                      |

| IFOUTN   | 62                       | 0   | IFVGA1 output: negative terminal                                                                     |

| IFOUTP   | 63                       | 0   | IFVGA1 output: positive terminal                                                                     |

| LDCAP    | 38                       | I/O | PLL lock detector decoupling capacitor pin                                                           |

| LESPI    | 72                       | I   | SPI latch enable                                                                                     |

| LOCKDET  | 5                        | 0   | PLL lock detect output (digital HIGH = locked, LOW = unlocked)                                       |

| MIXINDN  | 2                        | 0   | TX mixer output collector: negative terminal                                                         |

| MIXINDP  | 3                        | 0   | TX mixer output collector: positive terminal                                                         |

| PWRDET   | 4                        | 0   | Power alarm output (digital HIGH = output power above threshold; LOW = output power below threshold) |

| RDBKSPI  | 64                       | 0   | SPI data readback                                                                                    |

| REFIN    | 16                       | ı   | PLL reference clock input                                                                            |

| RXAGC    | 65                       | I   | RX AGC control input                                                                                 |

| RXBBCM   | 40                       | I   | RX chain common-mode input                                                                           |

| RXBBIN   | 43                       | 0   | RX baseband output I: negative terminal                                                              |

| RXBBIP   | 44                       | 0   | RX baseband output I: positive terminal                                                              |

| RXBBQN   | 41                       | 0   | RX baseband output Q: negative terminal                                                              |

| RXBBQP   | 42                       | 0   | RX baseband output Q: positive terminal                                                              |

| RXINN    | 69                       | I   | RX input: negative terminal                                                                          |

| RXINP    | 68                       | ı   | RX input: positive terminal                                                                          |

| RXLOTEST | 53                       | 0   | RX LO test pin                                                                                       |

| TEMPOUT  | 37                       | 0   | Temperature sensor output                                                                            |

| TXBBIN   | 21                       | I   | TX baseband I input: negative input                                                                  |

| TXBBIP   | 22                       | I   | TX baseband I input: positive input                                                                  |

| TXBBQN   | 19                       | 1   | TX baseband Q input: negative input                                                                  |

| TXBBQP   | 20                       | 1   | TX baseband Q input: positive input                                                                  |

## **PIN FUNCTIONS (continued)**

| PIN I/O  |     |     |                                           |

|----------|-----|-----|-------------------------------------------|

| NAME     | NO. | 1/0 | DESCRIPTION                               |

| TXLOTEST | 6   | 0   | TX LO test pin                            |

| TXOUTN   | 78  | 0   | TX IF output: negative terminal           |

| TXOUTP   | 77  | 0   | TX IF output: positive terminal           |

| TXPWD    | 1   | I   | TX power down                             |

| VCCDIGRX | 46  | -   | RX PLL digital power supply               |

| VCCDIGTX | 13  | -   | TX PLL digital power supply               |

| VCCIFIN  | 56  | _   | RX chain power supply                     |

| VCCPLLTX | 12  | -   | TX PLL power supply                       |

| VCCPLLRX | 47  | -   | RX PLL power supply                       |

| VCCREF   | 15  | -   | Reference clock power supply              |

| VCCRX    | 67  | _   | RX chain power supply                     |

| VCCSPI   | 75  | _   | SPI power supply                          |

| VCCTX    | 76  | -   | TX power supply                           |

| VCCVCORX | 52  | -   | RX VCO power supply                       |

| VCCVCOTX | 7   | -   | TX VCO power supply                       |

| VCCXPIC  | 29  | -   | XPIC power supply                         |

| VCCXPIC2 | 33  | -   | XPIC power supply                         |

| VTUNERX  | 50  | I   | RX VCO input control voltage              |

| VTUNETX  | 9   | I   | VCO tune voltage input                    |

| XPICAGC  | 30  | I   | XPIC AGC control input                    |

| XPICBBCM | 24  | _   | XPIC common-mode input                    |

| XPICBBIN | 27  | 0   | XPIC baseband I output: negative terminal |

| XPICBBIP | 28  | 0   | XPIC baseband I output: positive terminal |

| XPICBBQN | 25  | 0   | XPIC baseband Q output: negative terminal |

| XPICBBQP | 26  | 0   | XPIC baseband Q output: positive terminal |

| XPICINN  | 34  |     | XPIC input                                |

| XPICINP  | 35  | I   | XPIC input                                |

| XPICOUTN | 54  | 0   | XPIC output                               |

| XPICOUTP | 55  | 0   | XPIC output                               |

### **ABSOLUTE MAXIMUM RATINGS**(1)

|                  |                                    | VALUE      | UNIT |

|------------------|------------------------------------|------------|------|

|                  | Input voltage range <sup>(2)</sup> | -0.3 to 5  | V    |

|                  | ESD rating, HBM                    | 2000       | V    |

|                  | ESD rating, CDM                    | 500        | V    |

| TJ               | Junction temperature range         | -40 to 150 | °C   |

| T <sub>stg</sub> | Storage temperature range          | -65 to 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### THERMAL CHARACTERISTICS

Over recommended operating free-air temperature (unless otherwise noted)

|               | PARAMETER                             |                         | MIN | TYP | MAX | UNIT |

|---------------|---------------------------------------|-------------------------|-----|-----|-----|------|

| $\theta_{JA}$ | Thermal derating, junction-to-ambient | High-K board, still air |     | 8.5 |     | °C/W |

### RECOMMENDED OPERATING CONDITIONS

Over operating free-air temperature range (unless otherwise noted)

|                    |                                | MIN | TYP | MAX | UNIT |

|--------------------|--------------------------------|-----|-----|-----|------|

| V <sub>CC_3V</sub> | 3.3-V power-supply voltage     | 3   | 3.3 | 3.6 | V    |

| V_RXAGC            | Analog AGC voltage (pin 65)    | 0   |     | 2   | V    |

| V_XPICAGC          | Analog AGC voltage (pin 30)    | 0   |     | 1   | V    |

| T <sub>J</sub>     | Operating junction temperature | 0   | 65  | 125 | °C   |

| T <sub>A</sub>     | Operating ambient temperature  | -40 |     | 85  | °C   |

### **DC CHARACTERISTICS**

$V_{CC} = 3.3 \text{ V}; T_{J} = 65^{\circ}\text{C}$

|          | PARAMETER            | TEST CONDITIONS                  | MIN | TYP  | MAX | UNIT |

|----------|----------------------|----------------------------------|-----|------|-----|------|

|          |                      | TX on; RX on (SAW off); XPIC off |     | 947  |     |      |

| $I_{CC}$ | Total supply current | TX on; RX on (SAW on); XPIC off  |     | 965  |     | mA   |

|          |                      | TX on; RX on (SAW on); XPIC on   |     | 1085 |     |      |

### **DIGITAL INTERFACE CHARACTERISTICS**

$V_{CC} = 3.3 \text{ V}; T_{J} = 65^{\circ}\text{C}$

|                 | PARAMETER                 | TEST CONDITIONS | MIN                 | TYP MAX             | UNIT |

|-----------------|---------------------------|-----------------|---------------------|---------------------|------|

| $V_{IH}$        | High-level input voltage  |                 | 2                   | $V_{CC}$            | V    |

| $V_{IL}$        | Low-level input voltage   |                 | 0                   | 0.8                 | V    |

| V <sub>OH</sub> | High-level output voltage |                 | 0.8 V <sub>CC</sub> |                     | V    |

| V <sub>OL</sub> | Low-level output voltage  |                 |                     | 0.2 V <sub>CC</sub> | V    |

Product Folder Link(s): TRF2443

<sup>(2)</sup> All voltage values are with respect to network ground terminal.

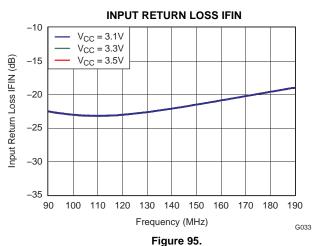

#### RECEIVER CHARACTERISTICS

$V_{CC~3V} = 3.3~V~\pm 5\%,~T_J = 65^{\circ}C$ , IF SAW filter insertion loss = 10 dB<sup>(1)</sup> (unless otherwise noted)

|                                 | PARAMETER                   | TEST CONDITIONS                          | MIN  | TYP  | MAX  | UNIT |

|---------------------------------|-----------------------------|------------------------------------------|------|------|------|------|

| f <sub>IF</sub>                 | Input IF frequency          |                                          |      | 140  |      | MHz  |

| From RX                         | _IN to RX_BBI/RX_ BBQ       |                                          |      |      |      | -    |

|                                 |                             | LNA_ATT = 0; RXAGC = 2 V <sup>(3)</sup>  | 76   | 86   |      |      |

| <b>o</b> (2)                    | Mandanina                   | LNA_ATT = 0; RXAGC = 2 V (4)             | 69   |      |      | -ID  |

| G <sub>max</sub> <sup>(2)</sup> | Maximum voltage gain        | LNA_ATT = 17; RXAGC = 2 V <sup>(3)</sup> | 59   | 68   |      | dB   |

|                                 |                             | LNA_ATT = 17; RXAGC = 2 V <sup>(4)</sup> | 52   |      |      |      |

|                                 |                             | LNA_ATT = 0; RXAGC = 0 V <sup>(3)</sup>  |      | 12   | 25   |      |

| <b>c</b> (2)                    | Minimum valtana nain        | LNA_ATT = 0; RXAGC = 0 V <sup>(4)</sup>  |      | 12   | 27   | dB   |

| G <sub>min</sub> <sup>(2)</sup> | Minimum voltage gain        | LNA_ATT = 17; RXAGC = 0 V <sup>(3)</sup> |      |      | 8    | ав   |

|                                 |                             | LNA_ATT = 17; RXAGC = 0 V <sup>(4)</sup> |      |      | 10   |      |

|                                 | LNA attenuation step        | LNA_ATT = 17 <sup>(5)</sup>              | 16.9 | 17.9 | 18.9 | dB   |

| ΔG <sub>step</sub>              | Digital gain step           | LNA attenuation setting through SPI      |      | 1.05 |      | dB   |

| $\Delta G_{range}$              | Analog gain range           | RXAGC from 0 V to 2 V <sup>(6)</sup>     | 54   | 62   |      | dB   |

|                                 | Gain flatness               | From 110 MHz to 170 MHz                  |      | 1.5  |      | dB   |

|                                 | Gain control slope          |                                          |      | 51   |      | dB/V |

| NE                              |                             | $LNA\_ATT = 0^{(8)(9)}$                  |      | 4.5  | 6    | 40   |

| NF                              | Noise figure <sup>(7)</sup> | LNA_ATT = $17^{(10)(11)}$                |      | 18.5 | 23   | dB   |

| IP3                             | Innut IDO                   | $LNA\_ATT = 0^{(12)(13)}$                |      | -9.5 |      | -ID  |

| IP3                             | Input IP3                   | LNA_ATT = $17^{(14)(15)}$                | 3    | 6.5  |      | dBm  |

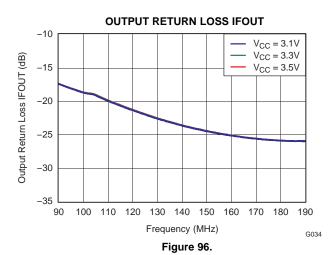

| Γin                             | Input return loss           | $Z_0 = 50 \Omega$ , differential         |      | -25  | -12  | dB   |

| FROM RX                         | (_IN TO IF_OUT              |                                          |      |      |      |      |

| G <sub>max</sub>                | Maximum voltage gain        |                                          |      | 33   |      | dB   |

| ΔG <sub>dig</sub>               | Digital gain range          | Programmed by SPI                        |      | 20   |      | dB   |

| ΔG <sub>step</sub>              | Digital gain step           |                                          |      | 1.05 |      | dB   |

| ΔG <sub>analog</sub>            | Analog gain range           |                                          |      | 34   |      | dB   |

|                                 | Noise figure                | LNA_ATT = 0, RXAGC = 2 V                 |      | 3.5  |      | dB   |

| NF                              | Noise figure                | LNA_ATT = 17, RXAGC = 2 V                |      | 19.5 |      | UD   |

| IP3                             | Input IP3                   | LNA_ATT = 0, RXAGC = 2 V                 |      | -13  |      | dBm  |

| Γin                             | Input return loss           | $Z_0 = 50 \Omega$ , differential         |      |      | -12  | dB   |

- (1) 10 dB includes SAW filter insertion loss plus matching/board loss

- (2) Gain measured from transformer input to RXBBI/Q output. External transformer insertion loss = 0.5 dB

- (3) SAW filter path enabled; baseband amplifier gain setting set to 9

- (4) SAW filter path disabled; baseband amplifier gain setting set to 0

- (5) Attenuation measured from LNA\_ATT = 0 state.

- (6) Monotonicity of RX gain versus VAGC is specified up to the maximum voltage gain spec and not the maximum VAGC voltage.

- (7) Automated test equipment 1-sigma measurement uncertainty of 0.15 dB.

- (8) SAW filter path disabled; baseband amplifier gain setting set to 0; total gain = 55 dB (gain measured from transformer input to RXBBI/Q output; external transformer insertion loss = 0.5 dB)

- (9) SAW filter path enabled; baseband amplifier gain setting set to 3; total gain = 66 dB (gain measured from transformer input to RXBBI/Q output; external transformer insertion loss = 0.5 dB)

- (10) SAW filter path disabled; baseband amplifier gain setting set to 0; total gain = 38 dB (gain measured from transformer input to RXBBI/Q output; external transformer insertion loss = 0.5 dB)

- (11) SAW filter path enabled; baseband amplifier gain setting set to 3; total gain = 49 dB (gain measured from transformer input to RXBBI/Q output; external transformer insertion loss = 0.5 dB)

- (12) SAW filter path enabled; baseband amplifier gain setting set to 9; total gain = 33 dB (gain measured from transformer input to RXBBI/Q output; external transformer insertion loss = 0.5 dB)

- (13) SAW filter path disabled; baseband amplifier gain setting set to 0; total gain = 35 dB (gain measured from transformer input to RXBBI/Q output; external transformer insertion loss = 0.5 dB)

- (14) SAW filter path enabled; baseband amplifier gain setting set to 9; total gain = 16 dB (gain measured from transformer input to RXBBI/Q output; external transformer insertion loss = 0.5 dB)

- (15) SAW filter path disabled; baseband amplifier gain setting set to 0; total gain = 18 dB (gain measured from transformer input to RXBBI/Q output; external transformer insertion loss = 0.5 dB)

## **RECEIVER CHARACTERISTICS (continued)**

$V_{CC\_3V} = 3.3~V~\pm 5\%,~T_J = 65^{\circ}C$  , IF SAW filter insertion loss = 10 dB (unless otherwise noted)

|                          | PARAMETER                  | TEST CONDITIONS                                                     | MIN TYP | MAX | UNIT |

|--------------------------|----------------------------|---------------------------------------------------------------------|---------|-----|------|

| FROM IF_                 | IN TO RX_BBI (OR RX_BBQ)   |                                                                     |         |     |      |

| G <sub>max</sub>         | Maximum voltage gain       | RXAGC = 2 V, RXBB_GAIN = 9                                          | 58      |     | dB   |

| $\Delta G_{dig}$         | Digital gain range         | Programmed by SPI                                                   | 24      |     | dB   |

| $\Delta G_{\text{step}}$ | Digital gain step          |                                                                     | 1       |     | dB   |

| $\Delta G_{analog}$      | Analog gain range          |                                                                     | 28      |     | dB   |

| NF                       | Naine figure               | RXAGC = 2 V, RXBB_GAIN = 9                                          | 12.5    |     | -10  |

|                          | Noise figure               | RXAGC = 0 V, RXBB_GAIN = 9                                          | 28      |     | dB   |

|                          | Image rejection            | See RX Image Rejection section                                      | -40     |     | dB   |

|                          | Output common mode         |                                                                     | 1.5     |     | V    |

|                          | December of customit load  | Parallel capacitor                                                  | 15      |     | pF   |

|                          | Baseband output load       | Parallel resistor                                                   | 1       |     | kΩ   |

| BASEBAN                  | ND LOW-PASS FILTER         |                                                                     |         |     |      |

| f <sub>C_ON</sub>        | 3-dB cutoff frequency      | Filter on, programmed via SPI                                       | 2       | 11  | MHz  |

| ATT <sub>30M</sub>       | Filter rejection at 30 MHz | Filter bypassed                                                     | 1       |     | dB   |

|                          |                            | 3-dB point with $f_C = 2.3$ MHz <sup>(16)</sup>                     | 2.2     |     | MHz  |

|                          |                            | 3-dB corner-frequency step <sup>(17)</sup>                          | 25      |     | kHz  |

|                          |                            | Rejection at 4.5 MHz with $f_C = 2.3$ MHz $^{(16)}$                 | 36      |     |      |

|                          |                            | Rejection at 8.75 MHz with f <sub>C</sub> = 2.3 MHz <sup>(16)</sup> | 76      |     | dB   |

|                          | Filter rejection           | Rejection at 17.5 MHz with f <sub>C</sub> = 2.3 MHz <sup>(16)</sup> | 80      |     |      |

|                          |                            | 3-dB point with $f_C = 8.5 \text{ MHz}^{(16)}$                      | 8.3     |     | MHz  |

|                          |                            | Rejection at 18 MHz with f <sub>C</sub> = 8.5 MHz <sup>(16)</sup>   | 30      |     |      |

|                          |                            | Rejection at 35 MHz with f <sub>C</sub> = 8.5 MHz <sup>(16)</sup>   | 65      |     | dB   |

|                          |                            | Rejection at 70 MHz with f <sub>C</sub> = 8.5 MHz <sup>(16)</sup>   | 80      |     |      |

Copyright © 2009, Texas Instruments Incorporated

<sup>(16)</sup> After room-temperature cutoff-frequency calibration (17) Baseband filter 3-dB corner frequency control step via SPI around  $f_C$  = 2.3 MHz

### TRANSMITTER CHARACTERISTICS

$V_{CC 3V} = 3.3 \text{ V} \pm 5\%$ ,  $T_J = 65^{\circ}\text{C}$  (unless otherwise noted)

|                    | PARAMETER                                           | TEST CONDITIONS                                         | MIN      | TYP         | MAX      | UNIT     |

|--------------------|-----------------------------------------------------|---------------------------------------------------------|----------|-------------|----------|----------|

| f <sub>lout</sub>  | TX output frequency                                 |                                                         |          | 340         |          | MHz      |

| FROM               | TXBBI/Q INPUTS TO TX RFOUT                          |                                                         | *        |             |          |          |

| P <sub>max</sub>   | Maximum output power                                | TX ATT set to 0 <sup>(1)</sup>                          | 2.5      |             |          | dBm      |

| P <sub>min</sub>   | Minimum output power                                | TX ATT set to 35                                        |          |             | -28.5    | dBm      |

| G <sub>range</sub> | Gain range                                          | Programmed by SPI                                       | 31       |             |          | dB       |

| G <sub>step</sub>  | 1-dB gain step                                      | Two consecutive 1-dB steps                              | 0.8      |             | 1.2      | dB       |

| N                  | Output poins floor                                  | TX ATT set to 4 <sup>(2)</sup>                          |          | -139        | -135     | dBm/Hz   |

| N <sub>out</sub>   | Output noise floor                                  | TX ATT set to 31 <sup>(2)</sup>                         |          | -166        | -162     | UDIII/HZ |

| OIP3               | Output ID2                                          | Two tones of –2.5 dBm each at TX output <sup>(3)</sup>  | 27.5     | 29.5        |          | dBm      |

| OIP3               | Output IP3                                          | Two tones of –29.5 dBm each at TX output <sup>(3)</sup> | 0.5      |             |          | аын      |

| CS                 | Carrier leakage                                     | Calibrated; TX ATT set to 4 <sup>(4)</sup>              |          | <b>-</b> 55 | -35      | dBm      |

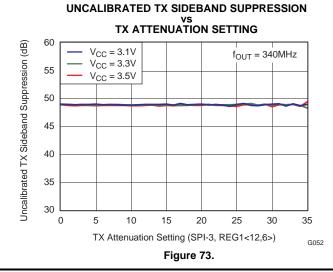

| SBS                | Side-band suppression                               | Uncalibrated <sup>(5)</sup>                             |          | -50         | -35      | dB       |

| HD2                | Second harmonic level                               | See <sup>(1)</sup>                                      |          | -55         |          | dBc      |

| HD3                | Third harmonic level                                | See <sup>(1)</sup>                                      |          | -50         |          | dBc      |

| τoff               | TX turnoff time <sup>(6)</sup>                      | TX_PWD: low $\rightarrow$ high;                         | 10       |             | 100      | μs       |

|                    | TX off attenuation <sup>(7)</sup>                   | TX_PWD = high                                           | 30       |             |          | dB       |

| VCM                | Baseband input common-mode voltage (8)              |                                                         |          | 1.4         |          | V        |

| 7                  | TV differential input impedance                     | Parallel resistor                                       |          | 10          |          | kΩ       |

| $Z_{BBin}$         | TX differential input impedance                     | Parallel capacitor                                      |          | 0.1         |          | pF       |

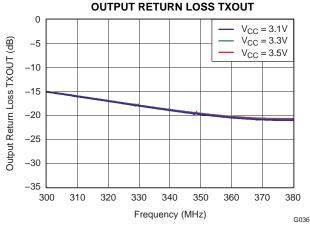

| Γout               | Output return loss                                  | $Z_0 = 50 \ \Omega^{(9)}$                               |          |             | -12      | dB       |

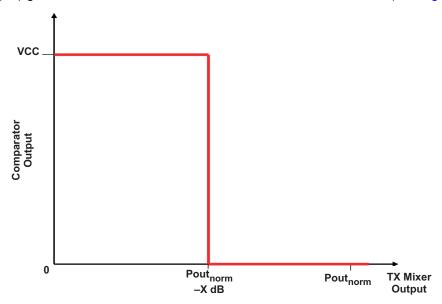

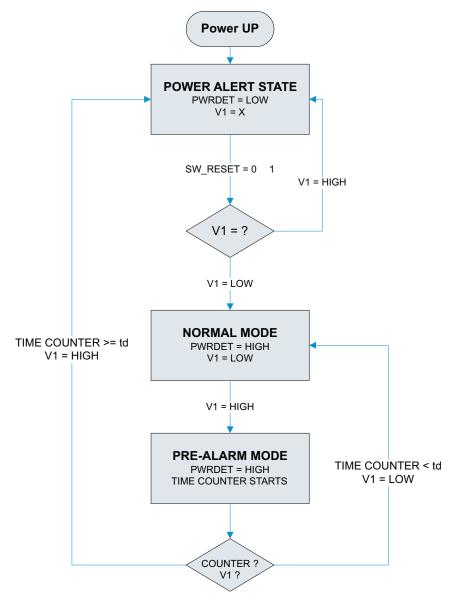

| POWER              | R ALARM DETECTOR (See the Power Alarm L             | Detector section)                                       |          |             |          |          |

|                    | Detector threshold                                  | See <sup>(10)</sup>                                     |          | See (11)    | See (11) | dB       |

|                    | Response time <sup>(12)</sup> (specified by design) |                                                         | See (11) |             |          | μs       |

- (1) Measured after the transformer (0.7-dB insertion loss) and with a TXBBI (or TXBBQ) input level of -23 dBVrms

- (2) No signal applied to TRF2443. This parameter is assured by characterization and is not production tested.

- (3) Two tones of –26 dBVrms each at TXBBI and TXBBQ inputs at 5 MHz and 8 MHz; measured at transformer output (0.7-dB insertion loss).

- (4) Using internal common and dc offset control

- (5) TXIQ\_PHASE set to 8; SPI-3, register 1, B<17,13>

- (6) See the TX Output Power Ramp-Down section.

- (7) Attenuation of output level from TX on.

- (8) Common mode input is set internally. It is possible to disable internal bias through SPI and apply external common mode.

- (9) Single-ended, measured at transformer output

- (10) Delta output power level at TX fixed gain that forces detector output low (power alarm).

- (11) Detector threshold and response time are fully programmable by the user. (See the Power Alarm Detector section.)

- (12) If output power is lower than threshold for more than user-specified value, power-alarm detector output goes low.

10

### RF SYNTHESIZER CHARACTERISTICS

$V_{CC 3V} = 3.3 \text{ V} \pm 5\%$ ,  $T_J = 65^{\circ}\text{C}$  (unless otherwise noted)

|                    | PARAMETER                      | TEST CONDITIONS                                                             | MIN  | TYP    | MAX  | UNIT       |  |

|--------------------|--------------------------------|-----------------------------------------------------------------------------|------|--------|------|------------|--|

| TXVCO              |                                |                                                                             | "    |        |      |            |  |

| f <sub>txvco</sub> | TXVCO frequency range          | See (1)                                                                     | 2640 |        | 2800 | MHz        |  |

| _                  |                                | Divide-by-8 mode                                                            | 330  |        | 350  |            |  |

| f <sub>txlo</sub>  | TXLO frequency range           | Divide-by-16 mode                                                           | 165  |        | 175  | MHz        |  |

|                    |                                | f <sub>out</sub> = 340 MHz; offset = 10 kHz                                 |      | -92.5  |      |            |  |

|                    | TXLO free-running phase noise  | f <sub>out</sub> = 340 MHz; offset = 100 kHz                                | _    | -117.5 |      |            |  |

|                    |                                | f <sub>out</sub> = 340 MHz; offset = 1 MHz                                  |      | -140   |      | dBc/Hz     |  |

|                    |                                | f <sub>out</sub> = 340 MHz; offset = 20 MHz                                 |      | -150   |      |            |  |

| Kv <sub>TX</sub>   | TXVCO gain                     |                                                                             |      | 45     |      | MHz/V      |  |

| TXPLL              |                                |                                                                             | "    |        |      |            |  |

| f <sub>PFD</sub>   | PFD frequency                  |                                                                             |      | 20     |      | MHz        |  |

|                    |                                | f <sub>out</sub> = 340 MHz; offset = 20 kHz                                 |      | -117   |      |            |  |

|                    |                                | f <sub>out</sub> = 340 MHz; offset = 100 kHz                                |      | -116   |      | ID // I    |  |

|                    | TXLO closed-loop phase noise   | f <sub>out</sub> = 340 MHz; offset = 1 MHz                                  |      | -140   |      | dBc/Hz     |  |

|                    |                                | f <sub>out</sub> = 340 MHz; offset = 20 MHz                                 |      | -150   |      |            |  |

|                    | Integrated TXLO noise          | Integrated from 1 kHz to 12 MHz; f <sub>out</sub> = 340 MHz <sup>(2)</sup>  |      | -56.5  |      | dB         |  |

|                    | Reference spur                 | Measured at TXLOTEST (2720 MHz)                                             |      |        | -70  | dBc        |  |

|                    | Lock time                      | From unlocked state to locked state (includes digital-calibration time) (3) |      | 300    |      | μs         |  |

|                    |                                | f <sub>out</sub> = 165 MHz; offset = 20 kHz                                 |      | -121   |      |            |  |

|                    | TXLO closed-loop phase noise   | f <sub>out</sub> = 165 MHz; offset = 100 kHz                                |      | -120   |      | -ID - /L I |  |

|                    |                                | f <sub>out</sub> = 165 MHz; offset = 1 MHz                                  |      | -141   |      | dBc/Hz     |  |

|                    |                                | f <sub>out</sub> = 165 MHz; offset = 20 MHz                                 |      | -147   |      |            |  |

| Vcc <sub>min</sub> | PLL-lock minimum power supply  | $T_J = 65^{\circ}C$                                                         | 2.8  |        |      | V          |  |

| RXVCO              |                                |                                                                             | •    |        |      |            |  |

| f <sub>rxvco</sub> | RXVCO frequency range          | See <sup>(1)</sup>                                                          | 2240 |        | 2640 | MHz        |  |

|                    | DVI O fraguency range          | Divide-by-8 mode                                                            | 280  |        | 330  | NAL I-     |  |

| f <sub>rxlo</sub>  | RXLO frequency range           | Divide-by-16 mode                                                           | 140  |        | 165  | MHz        |  |

|                    |                                | f <sub>out</sub> = 140 MHz; offset = 10 kHz                                 |      | -97.5  |      |            |  |

|                    | DVI O free rupping phase poice | f <sub>out</sub> = 140 MHz; offset = 100 kHz                                | -    | -122.5 |      | dBc/Hz     |  |

|                    | RXLO free-running phase noise  | f <sub>out</sub> = 140 MHz; offset = 1 MHz                                  |      | -146   |      | UDC/11Z    |  |

|                    |                                | f <sub>out</sub> = 140 MHz; offset = 20 MHz                                 |      | -150   |      |            |  |

| $Kv_{RX}$          | RXVCO gain                     |                                                                             |      | 45     |      | MHz/V      |  |

| RXPLL              |                                |                                                                             |      |        |      |            |  |

| f <sub>PFD</sub>   | PFD frequency                  |                                                                             |      | 20     |      | MHz        |  |

|                    | Integrated RXLO noise          | Integrated from 1 kHz to 12 MHz; f <sub>out</sub> = 140 MHz <sup>(2)</sup>  |      | -62    |      | dB         |  |

|                    | integrated NALO noise          | Integrated from 1 kHz to 12 MHz; f <sub>out</sub> = 160 MHz <sup>(2)</sup>  |      | -60    |      | uБ         |  |

|                    |                                | f <sub>out</sub> = 140 MHz; offset = 20 kHz                                 |      | -122   |      |            |  |

|                    | RXLO closed-loop phase noise   | f <sub>out</sub> = 140 MHz; offset = 100 kHz                                |      | -121   |      | dBc/Hz     |  |

|                    | MALO GIOSEU-100P PHASE HOISE   | f <sub>out</sub> = 140 MHz; offset = 1 MHz                                  |      | -146   |      | UDC/TIZ    |  |

|                    |                                | f <sub>out</sub> = 140 MHz; offset = 20 MHz                                 |      | -150   |      | 1          |  |

|                    | Reference spur                 | Measured at RXLOTEST (2240 MHz)                                             |      |        | -65  | dBc        |  |

|                    | Lock time                      | From unlock state to lock state (includes digital-calibration time) (3)     |      | 300    |      | μs         |  |

|                    |                                |                                                                             |      |        |      |            |  |

Product Folder Link(s): TRF2443

Frequency range proven locked with PFD frequency = 20 MHz

Optimized for lowest integrated noise; see the *Reference-Clock Characteristics* table for recommended reference clock performance.

Charge-pump current = 1 mA, PFD frequency = 20 MHz, loop filter optimized (see *Application Schematic* section)

### REFERENCE-CLOCK CHARACTERISTICS

$V_{CC} = 3.3 \text{ V}$

|             | PARAMETER                   | TEST CONDITIONS                                        | MIN | TYP  | MAX | UNIT            |  |

|-------------|-----------------------------|--------------------------------------------------------|-----|------|-----|-----------------|--|

| $f_{ref}$   | Reference frequency         |                                                        |     | 20   |     | MHz             |  |

| Phase noise |                             | 1 kHz                                                  |     | -135 |     | -ID - /I I-     |  |

|             | Priase noise                | Floor                                                  |     | -160 |     | dBc/Hz          |  |

|             | Reference-clock input level | REFIN pin, ac-coupled on board (internally dc-coupled) | 0.8 | 2    | 3   | V <sub>PP</sub> |  |

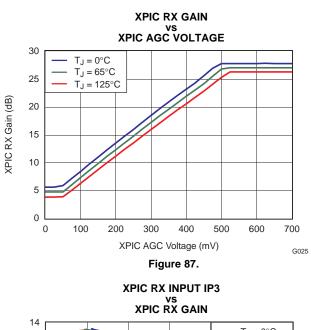

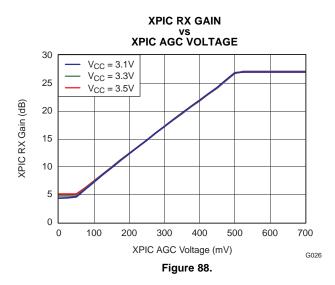

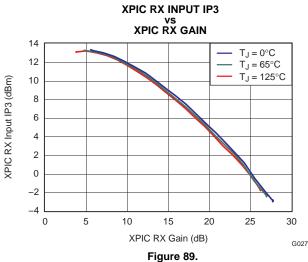

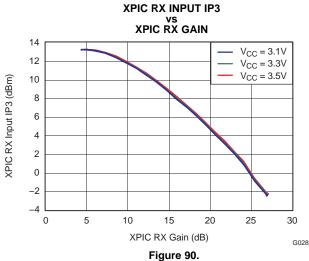

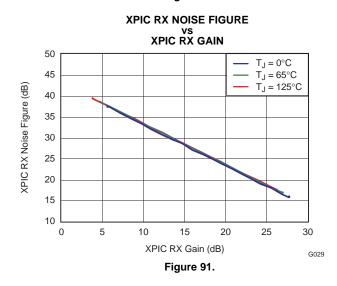

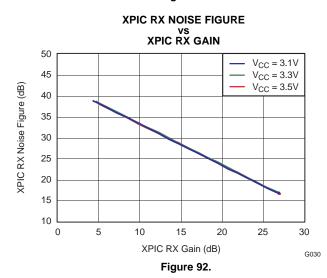

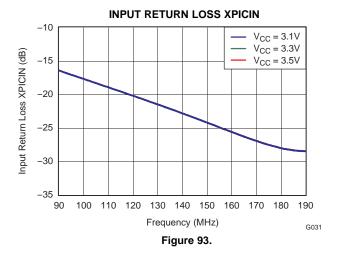

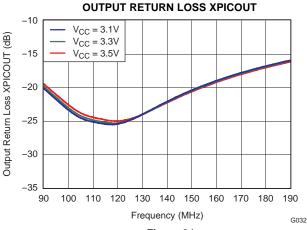

### **XPIC CHARACTERISTICS**

$V_{CC_3V} = 3.3 \text{ V} \pm 5\%$ ,  $T_J = 65^{\circ}\text{C}$  (unless otherwise noted)

|                     | PARAMETER               | TEST CONDITIONS                                                       | MIN  | TYP | MAX | UNIT |

|---------------------|-------------------------|-----------------------------------------------------------------------|------|-----|-----|------|

| From RX_            | IN to XPIC_OUT          |                                                                       |      |     |     |      |

| f <sub>in</sub>     | Input frequency         |                                                                       |      | 140 |     | MHz  |

| P <sub>out</sub>    | Output power            | $P_{in} = -32$ dBm, LNA ATT set to $0^{(1)}$                          | -14  | -12 | -10 | dBm  |

|                     | Output power flatness   | From 110 MHz to 170 MHz                                               |      | 1   |     | dB   |

| NF                  | Noise figure            | LNA ATT set to 0, total gain = 20 dB                                  |      | 15  | 22  | dB   |

| OIP3                | Output IP3              | Two tones of –16 dBm each at 136 MHz and 144 MHz $^{(1)}$ $^{(2)(3)}$ | 11.5 | 13  |     | dBm  |

| Γout                | Output return loss      | $Z_0 = 75 \Omega$ , single-ended                                      |      |     | -12 | dB   |

| FROM XP             | IC_IN TO XPIC_BBI/Q     |                                                                       |      |     |     |      |

| G <sub>MAX</sub>    | Maximum gain (4)        | XPIC_AGC = 0.7 V and XPICBB_GAIN set to 2                             | 21   | 27  |     | dB   |

| G <sub>MIN</sub>    | Minimum gain (4)        | XPIC_AGC = 0 V and XPICBB_GAIN set to 2                               |      | 5   | 10  | dB   |

|                     | Gain control slope      |                                                                       |      | 46  |     | dB/V |

| G <sub>DRange</sub> | Digital gain range      | Programmed via SPI                                                    |      | 11  |     | dB   |

|                     | Gain flatness           | Measured over 110 MHz to 170 MHz                                      |      | 1   |     | dB   |

| NF                  | Noise figure            | XPICBB_GAIN set to 2; total gain = 21 dB                              |      | 22  | 25  | dB   |

| IDO                 | Legarit IDO             | XPICBB_GAIN set to 2; total gain = 21 dB                              | -4   | 0   |     | .ID  |

| IP3                 | Input IP3               | XPICBB_GAIN set to 2; total gain = 10 dB                              | 6    | 9.5 |     | dBm  |

|                     | Image rejection         | See RX Image Rejection section                                        |      | -40 |     | dB   |

| Γin                 | Input return loss       | $Z_0 = 75 \Omega$ , single-ended                                      |      |     | -12 | dB   |

|                     | Output common mode      |                                                                       |      | 1.5 |     | V    |

|                     | December of autout load | Parallel capacitor                                                    |      | 15  |     | pF   |

|                     | Baseband output load    | Parallel resistor                                                     |      | 1   |     | kΩ   |

<sup>(1)</sup> RXAGC voltage to have RXBBI (or RXBBQ) output level = -17 dBVrms

<sup>(2)</sup> LNA ATT set to 0; total power gain = 20 dB

(3) Measured at XPIC\_OUT balun output (75-Ω characteristic impedance)

(4) Measured from differential output (XPICBBIP/N or XPICBBQP/N) to XPICINN input balun

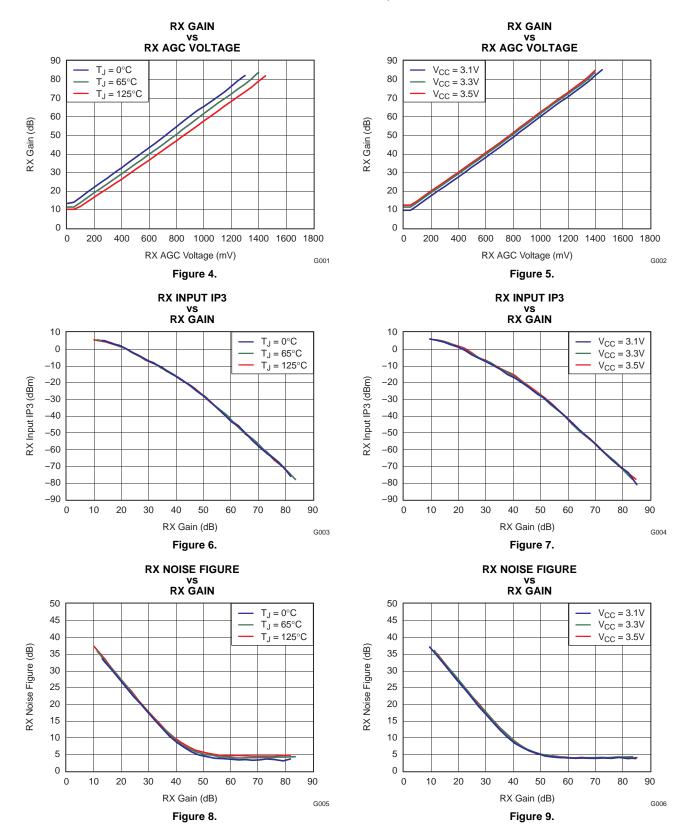

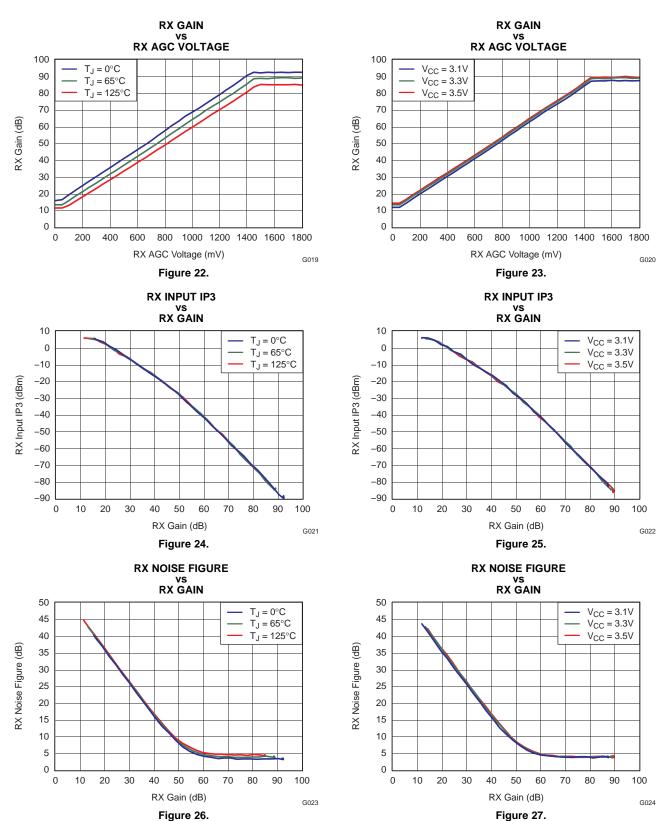

$f_{in}$ = 140 MHz, SAW\_EN = 0, LNA\_ATT = 0, baseband gain setting = 0, 3-dB pad enabled ( $T_J$  = 65°C,  $V_{CC}$  = 3.3 V, unless otherwise noted)

$f_{in}$ = 140 MHz, SAW\_EN = 1, LNA\_ATT = 0, baseband gain setting = 3, 3-dB pad disabled (T<sub>J</sub> = 65°C, V<sub>CC</sub> = 3.3 V, unless otherwise noted)

$f_{in}$ = 140 MHz, SAW\_EN = 1, LNA\_ATT = 0, baseband gain setting = 6, 3-dB pad disabled (T<sub>J</sub> = 65°C, V<sub>CC</sub> = 3.3 V, unless otherwise noted)

$f_{in}$ = 140 MHz, SAW\_EN = 1, LNA\_ATT = 0, baseband gain setting = 9, 3-dB pad disabled (T<sub>J</sub> = 65°C, V<sub>CC</sub> = 3.3 V, unless otherwise noted)

$f_{in}$ = 140 MHz ( $T_J$  = 65°C,  $V_{CC}$  = 3.3 V, unless otherwise noted)

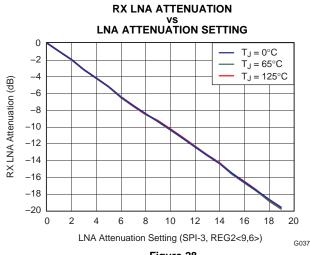

Figure 28.

Figure 29.

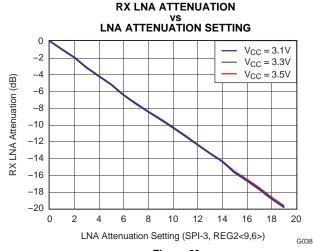

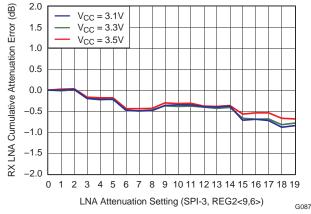

### **RX LNA CUMULATIVE ATTENUATION ERROR** LNA ATTENUATION SETTING

Figure 30.

# **RX LNA CUMULATIVE ATTENUATION ERROR** LNA ATTENUATION SETTING $V_{CC} = 3.1V$

Figure 31.

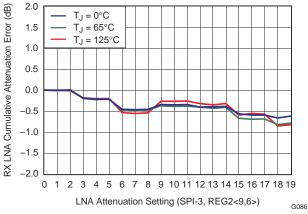

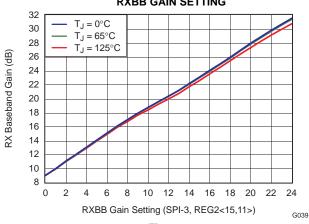

# **RX BASEBAND GAIN** vs RXBB GAIN SETTING

Figure 32.

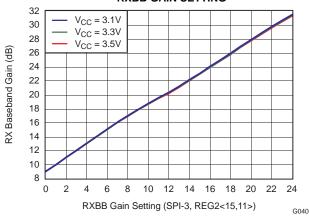

## **RX BASEBAND GAIN** vs RXBB GAIN SETTING

Figure 33.

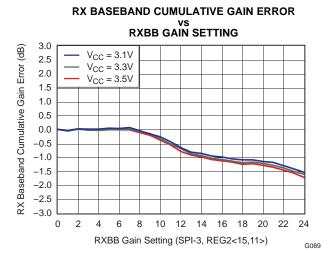

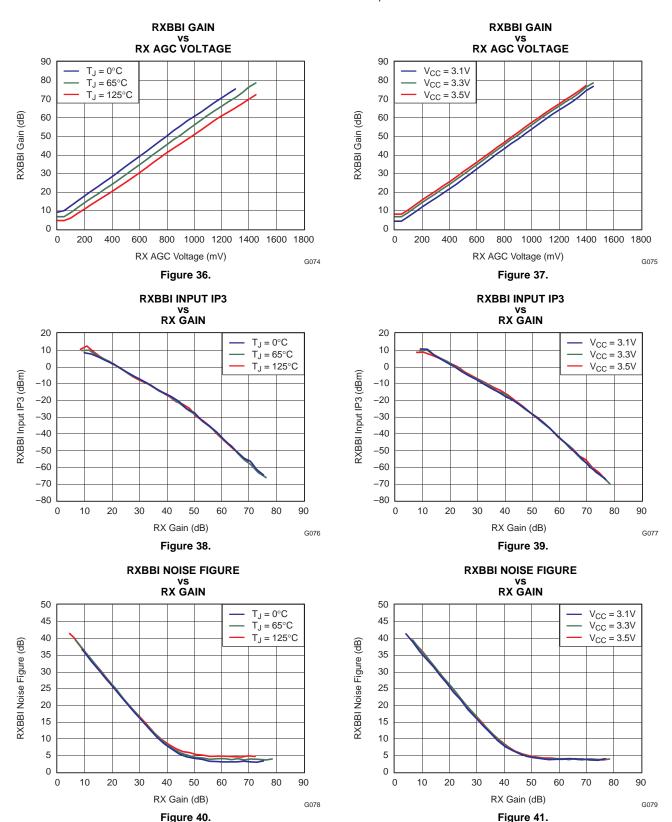

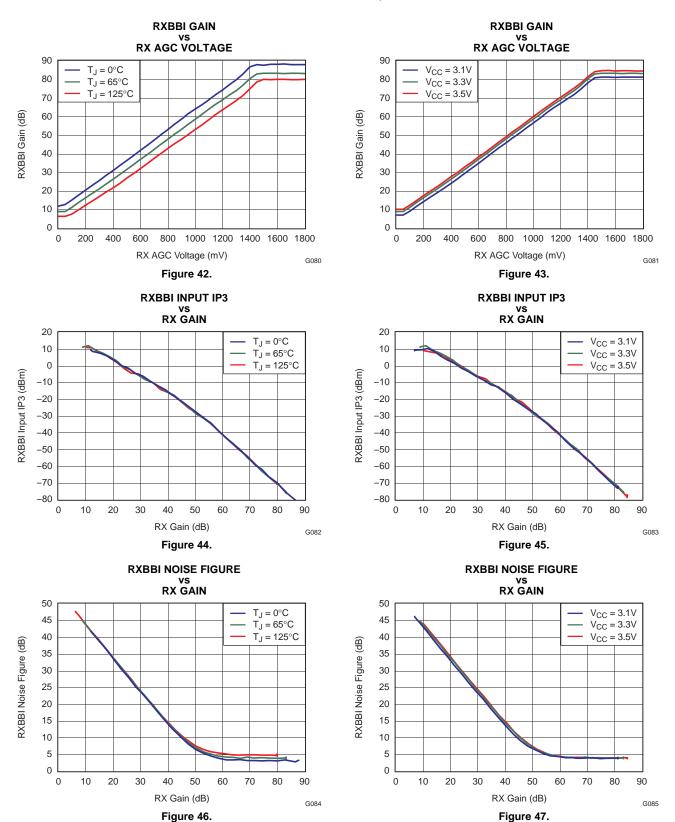

## RECEIVER TYPICAL CHARACTERISTICS (continued)

$f_{in}$ = 140 MHz ( $T_J$  = 65°C,  $V_{CC}$  = 3.3 V, unless otherwise noted)

#### **RX BASEBAND CUMULATIVE GAIN ERROR** vs RXBB GAIN SETTING 3.0 Error (dB) $T_J = 0^{\circ}C$ 2.5 $T_J = 65$ °C $T_J = 125$ °C 2.0 1.5 RX Baseband Cumulative Gain 1.0 0.5 0.0 -0.5 -1.0 -1.5 -2.0 -2.5 -3.08 10 12 14 16 18 20 0 RXBB Gain Setting (SPI-3, REG2<15,11>)

### Figure 34.

Figure 35.

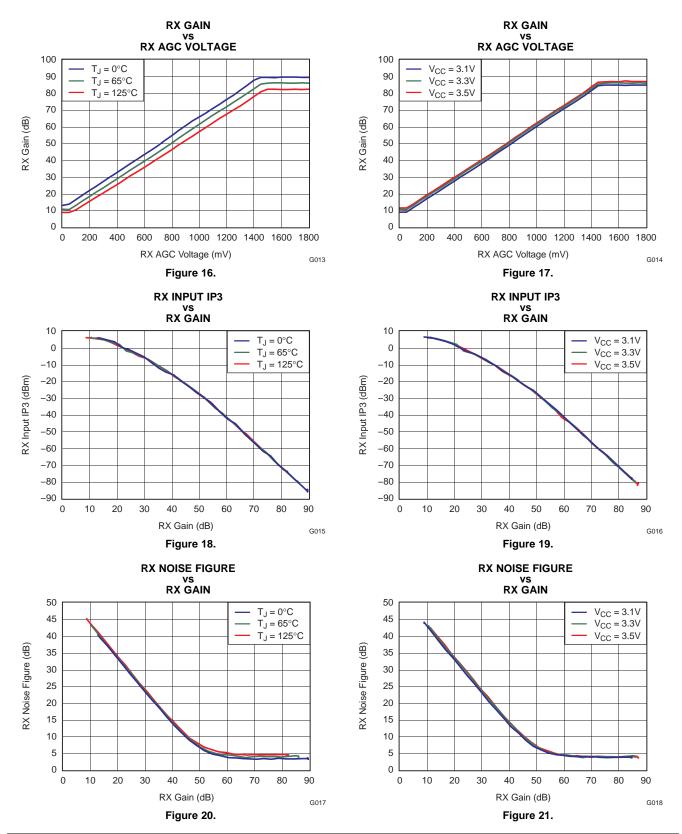

$f_{in}$ = 280 MHz, SAW\_EN = 0, LNA\_ATT = 0, baseband gain setting = 0, 3-dB pad enabled (T<sub>J</sub> = 65°C, V<sub>CC</sub> = 3.3 V, unless otherwise noted)

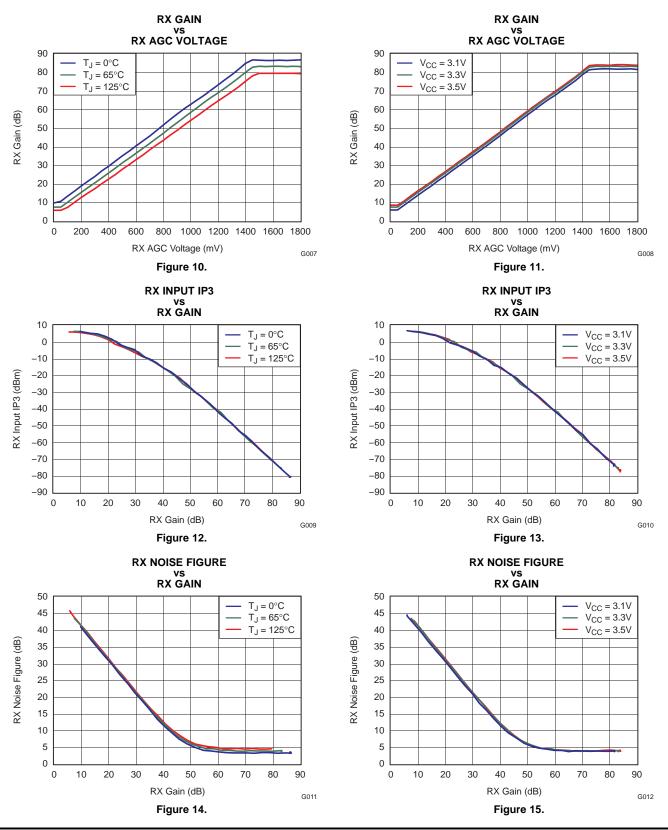

$f_{in}$ = 280 MHz, SAW\_EN = 1, LNA\_ATT = 0, baseband gain setting = 9, 3-dB pad disabled (T<sub>J</sub> = 65°C, V<sub>CC</sub> = 3.3 V, unless otherwise noted)

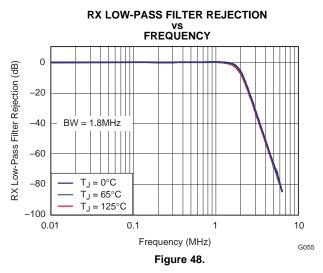

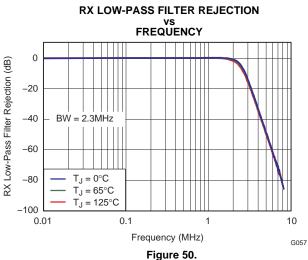

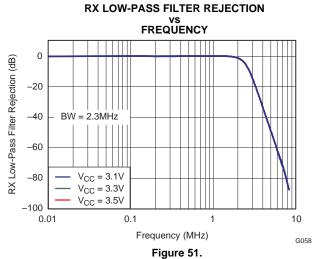

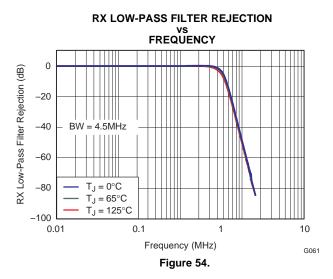

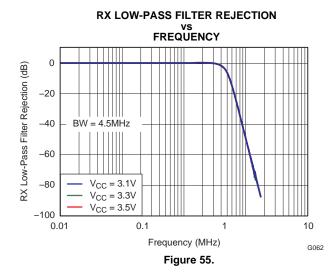

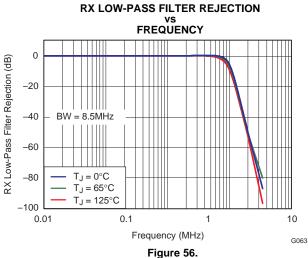

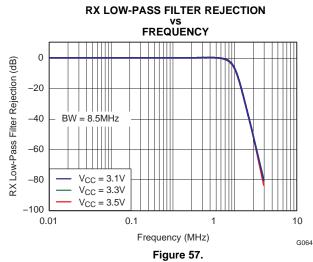

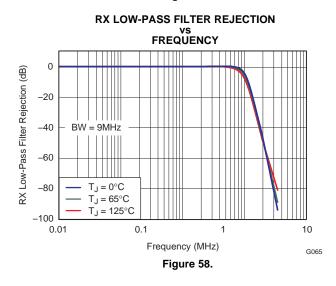

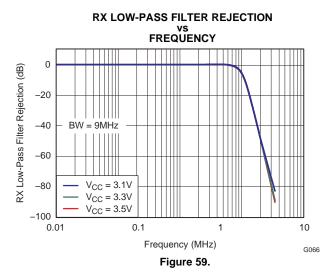

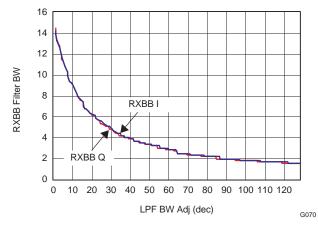

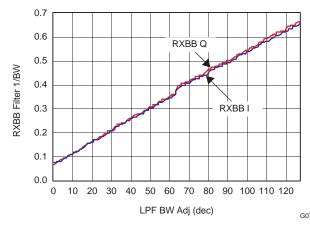

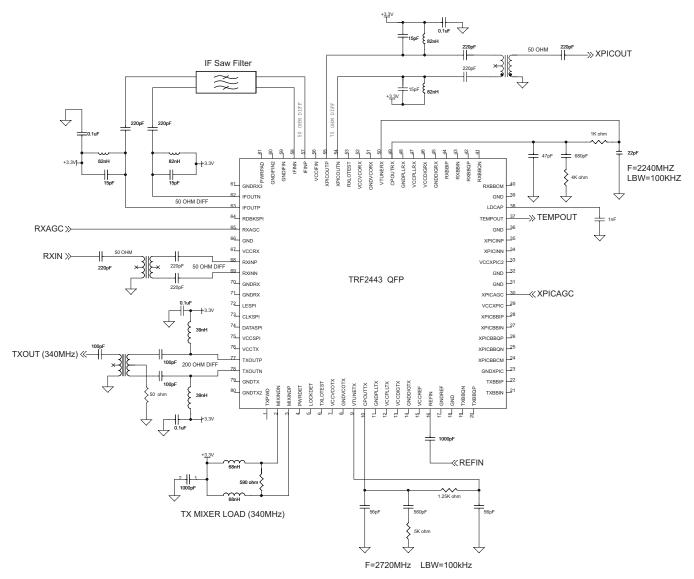

### RECEIVER LOW-PASS FILTER TYPICAL CHARACTERISTICS

$(T_J = 65^{\circ}C, V_{CC} = 3.3 \text{ V}, \text{ unless otherwise noted})$

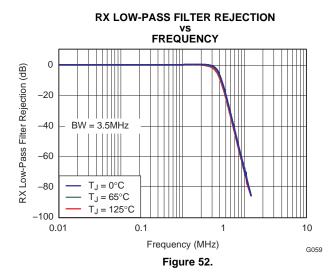

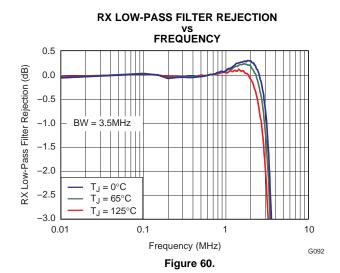

## RECEIVER LOW-PASS FILTER TYPICAL CHARACTERISTICS (continued)

$(T_J = 65$ °C,  $V_{CC} = 3.3$  V, unless otherwise noted)

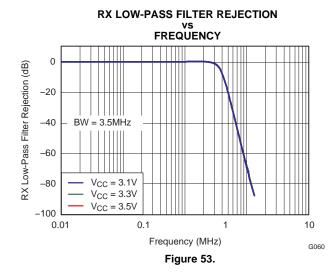

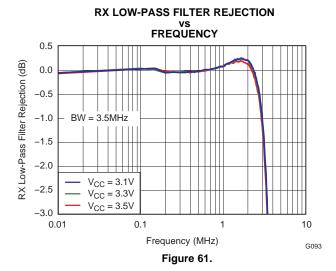

### RECEIVER LOW-PASS FILTER TYPICAL CHARACTERISTICS (continued)

$(T_J = 65$ °C,  $V_{CC} = 3.3$  V, unless otherwise noted)

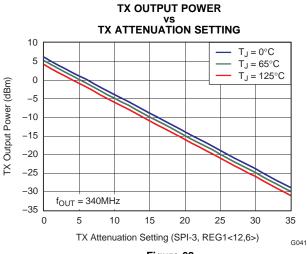

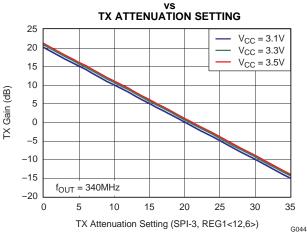

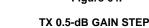

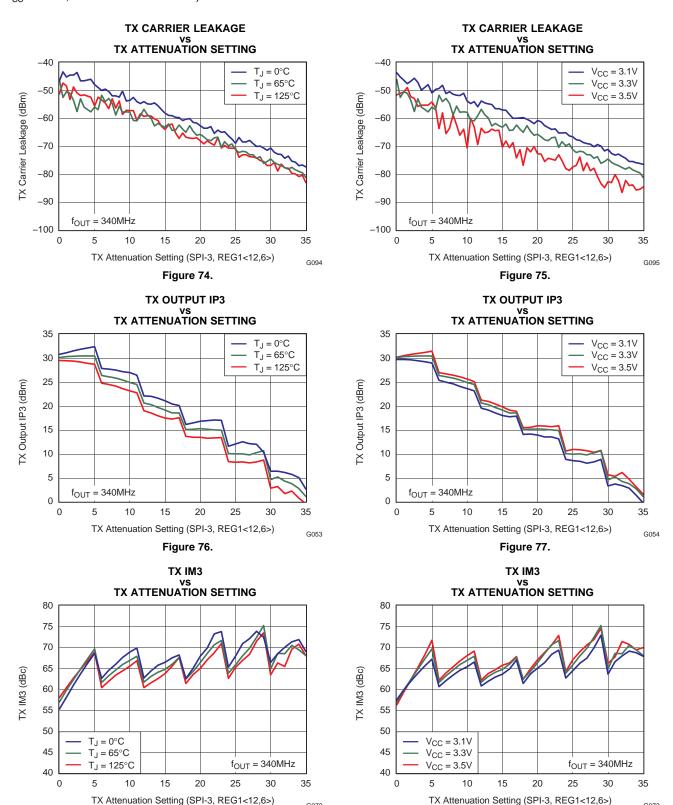

### TRANSMITTER TYPICAL CHARACTERISTICS

Measured after the transformer (0.7-dB insertion loss) and with a TXBBI/TXBBQ input level of -23 dBVrms (T<sub>J</sub> = 65°C,  $V_{CC} = 3.3 \text{ V}$ , unless otherwise noted)

10  $V_{CC} = 3.1V$ 5  $V_{CC} = 3.3V$  $V_{CC} = 3.5V$ 0 TX Output Power (dBm) -5 -10 -15 -20 -25 -30  $f_{OUT} = 340MHz$ -35 35 0 15 20 25 30 TX Attenuation Setting (SPI-3, REG1<12,6>) G042

TX OUTPUT POWER

vs TX ATTENUATION SETTING

Figure 62.

**TX GAIN** TX ATTENUATION SETTING 25  $T_J = 0^{\circ}C$ 20  $T_J = 65^{\circ}C$  $T_J = 125^{\circ}C$ 15 10 5 0

**TX GAIN**

Figure 63.

Figure 64.

TX Attenuation Setting (SPI-3, REG1<12,6>)

20

25

30

35

G043

15

Figure 65.

Figure 67.

TX Gain (dB)

-5 -10

-15

-20

0

$f_{OUT} = 340MHz$

10

5

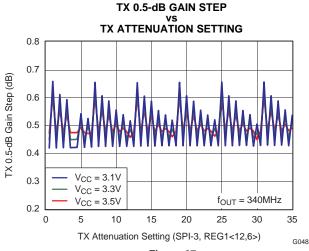

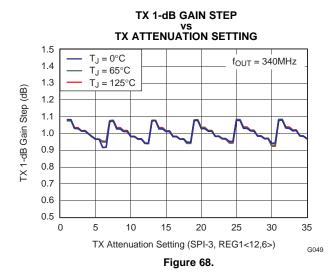

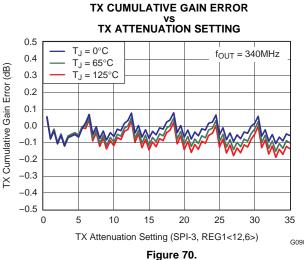

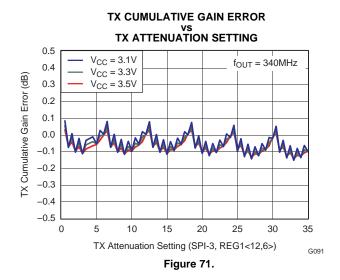

## TRANSMITTER TYPICAL CHARACTERISTICS (continued)

Measured after the transformer (0.7-dB insertion loss) and with a TXBBI/TXBBQ input level of -23 dBVrms ( $T_J = 65^{\circ}$ C,  $V_{CC} = 3.3$  V, unless otherwise noted)

TX 1-dB GAIN STEP vs TX ATTENUATION SETTING 1.5  $V_{CC} = 3.1V$  $f_{OUT} = 340MHz$ 1.4  $V_{CC} = 3.3V$ 1.3  $V_{CC} = 3.5V$ 1.2 TX 1-dB Gain Step 1.1 1.0 0.9 8.0 0.7 0.6 0.5 0 10 15 20 30 35 TX Attenuation Setting (SPI-3, REG1<12,6>) G050 Figure 69.

#### vs TX ATTENUATION SETTING 60 Uncalibrated TX Sideband Suppression (dB) $T_J = 0^{\circ}C$ $f_{OUT} = 340MHz$ T<sub>J</sub> = 65°C 55 $T_{.1} = 125^{\circ}C$ 50 45 40 35 30 0 10 15 20 30 35 TX Attenuation Setting (SPI-3, REG1<12,6>) G051 Figure 72.

**UNCALIBRATED TX SIDEBAND SUPPRESSION**

## TRANSMITTER TYPICAL CHARACTERISTICS (continued)

Measured after the transformer (0.7-dB insertion loss) and with a TXBBI/TXBBQ input level of -23 dBVrms (T<sub>J</sub> = 65°C,  $V_{CC} = 3.3 \text{ V}$ , unless otherwise noted)

Figure 78.

Figure 79.

G073

G072

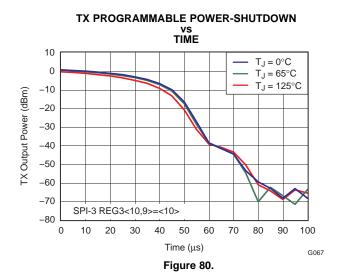

### TRANSMITTER TYPICAL CHARACTERISTICS (continued)

Measured after the transformer (0.7-dB insertion loss) and with a TXBBI/TXBBQ input level of -23 dBVrms ( $T_J = 65^{\circ}$ C,  $V_{CC} = 3.3$  V, unless otherwise noted)

#### TX PROGRAMMABLE POWER-SHUTDOWN vs TIME 10 $V_{CC} = 3.1V$ 0 $V_{CC} = 3.3V$ $V_{CC} = 3.5V$ -10 TX Output Power (dBm) -20 -30 -40 -50 -60 -70 SPI-3 REG3<10.9>=<10> -80 10 20 50 60 80 90 100 Time (µs) G068

Figure 81.

#### **TX OUTPUT NOISE** vs TX ATTENUATION SETTING -120 $V_{CC} = 3.1V$ $V_{CC} = 3.3V$ -125 $V_{CC} = 3.5V$ -130 TX Output Noise (dBm/Hz) -135 -140 -145 -150 -155 -160 -165 Note: No Input Signal -170 30 TX Attenuation Setting (SPI-3, REG1<12,6>) G069

### PLL TYPICAL CHARACTERISTICS

Measured at TXLOTEST pin (6) and RXLOTEST pin (53). Charge-pump current = 1 mA, PFD frequency = 20 MHz, loop filter optimized (see *Application Schematic* section). ( $T_J = 65^{\circ}$ C,  $V_{CC} = 3.3$  V, unless otherwise noted)

$f_{in}$ = 140 MHz, XPIC baseband gain setting = 2 ( $T_J$  = 65°C,  $V_{CC}$  = 3.3 V, unless otherwise noted)

Copyright © 2009, Texas Instruments Incorporated

### INSERTION LOSSES TYPICAL CHARACTERISTICS

Measured after transformers (see Application Schematic section). (T<sub>J</sub> = 65°C, V<sub>CC</sub> = 3.3 V, unless otherwise noted)

INPUT RETURN LOSS RXIN

Figure 98.

#### **SPI REGISTERS**

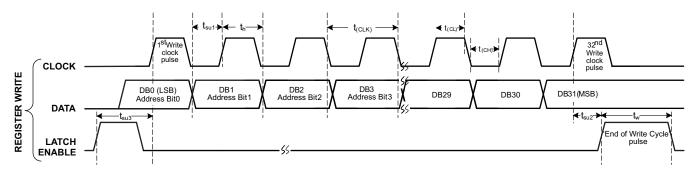

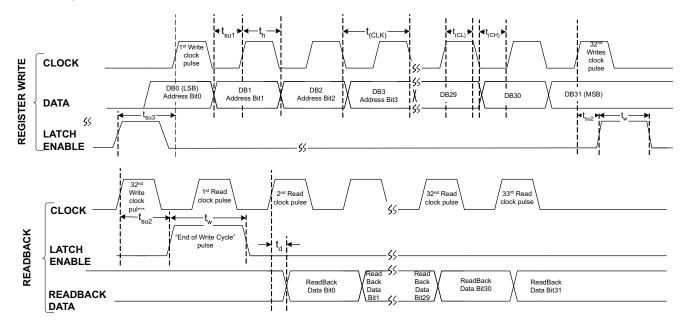

The TRF2443 features a three-wire serial programming interface (SPI) that controls an internal 32-bit shift register. There are a total of three signals that must be applied: the clock (CLKSPI), the serial data (DATASPI) and the latch enable (LESPI). The TRF2443 has an additional pin (RDBKSPI) for readback functionality. This pin is a digital pin and can be used to read back values of different internal registers.

The DATA (DB0-DB31) is loaded LSB-first and is read on the rising edge of the CLOCK. The latch enable is asynchronous to the CLOCK, and at its rising edge the data in the shift register is loaded onto the selected internal register. The 5 LSBs of the data field are the address bits to select the available internal registers (see Figure 99).

The SPI can operate reliably at clock speeds up to 20 MHz (clock period <50 ns). In theory, two 32-bit registers could be programmed within 3.3  $\mu$ s (64 clock cycles at 50 ns per clock cycle plus setup times). However, the user must exercise care when writing consecutive registers to ensure that subsequent register writes do not disrupt a previously requested operation such as a calibration. Calibration times are functions of the external reference frequency used as well as internally programmable clock dividers set by the user. The application section of this data sheet describes how to determine these calibration times. The user should allow for such calibration times when writing registers to the serial interface that contain settings related to the calibration or settings related to the circuits which are being calibrated.

Figure 99. SPI Timing Diagram

Table 1. SPI Timing – Writing Phase

| SYMBOL             | PARAMETER                   | MIN | TYP | MAX | UNITS |

|--------------------|-----------------------------|-----|-----|-----|-------|

| t <sub>h</sub>     | Hold time, data to clock    | 20  |     |     | ns    |

| t <sub>SU1</sub>   | Setup time, data to clock   | 20  |     |     | ns    |

| t <sub>(CL)</sub>  | Clock low duration          | 20  |     |     | ns    |

| t <sub>(CH)</sub>  | Clock high duration         | 20  |     |     | ns    |

| t <sub>SU2</sub>   | Setup time, clock to enable | 20  |     |     | ns    |

| t <sub>W</sub>     | Enable Time                 | 50  |     |     | ns    |

| t <sub>(CLK)</sub> | Clock period                | 50  |     |     | ns    |

| t <sub>SU3</sub>   | Setup time, latch to data   | 70  |     |     | ns    |

### **TRF2443 Addressing Scheme**

Copyright © 2009, Texas Instruments Incorporated

The TRF2443 has a separate set of register banks for the EEPROM (SPI-0), TX PLL (SPI-1), RX PLL (SPI-2), and TX/RX functionality (SPI-3). Each of the register banks has unique address bits to identify it, and within each register bank there are several registers which require an additional 3 bits of addressing.

Each register is 32 bits long; the bits can be described by B<31,0>. The 5 LSBs of each register, (B<4,0>), are the address bits, with B<4,3> corresponding to the address of the register bank and B<2,0> corresponding to the address of the individual register within each bank (see Table 2).

Product Folder Link(s): TP

Table 2. SPI Register Bank Addresses

| REGISTER BANK | ADDRESS | NUMBER OF<br>REGISTERS |

|---------------|---------|------------------------|

| EEPROM        | 00      | 3                      |

| TX PLL        | 01      | 6                      |

| RX PLL        | 10      | 6                      |

| TX/RX         | 11      | 8                      |

**Table 3. SPI Register Addresses**

|              |     | NAME              | POWER-ON<br>VALUE | SUGGESTED<br>VALUE | DESCRIPTION                                                                                                                                                                                                                             |

|--------------|-----|-------------------|-------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | B0  | ADDR <0>          | Х                 | X                  | Register address: B<2,0>                                                                                                                                                                                                                |

|              | B1  | ADDR <1>          | X                 | X                  | For PLLs (SPI-1 and SPI-2):                                                                                                                                                                                                             |

|              | B2  | ADDR <2>          | X                 | X                  | Reg 0(000), Reg 1(001), Reg 2 (010), Reg 3 (011), Reg 4 (100), Reg 5 (101)                                                                                                                                                              |

| Address bits | 50  | 1000              |                   |                    | For TX_RX (SPI-3):  Reg 0 (000), Reg 1(001), Reg 2 (010), Reg 3 (011), Reg 4 (100), Reg 5 (101), Reg 6(110), Reg 7(111)  (Note: In TX_RX (SPI-3), Reg 0 has special functionality as described in the TX and RX SPI Registers section.) |

|              | B3  | ADDR <3>          | X                 | X                  | Register bank: B<4,3>                                                                                                                                                                                                                   |

|              | B4  | ADDR <4>          | Х                 | Х                  | TX PLL (01); RX PLL (10); TX_RX (11)                                                                                                                                                                                                    |

|              | B5  | Data bit<br>(LSB) | Х                 | X                  |                                                                                                                                                                                                                                         |

|              | B6  | Data bit          | Х                 | X                  |                                                                                                                                                                                                                                         |

|              | B7  | Data bit          | Х                 | X                  |                                                                                                                                                                                                                                         |

|              | B8  | Data bit          | Х                 | X                  |                                                                                                                                                                                                                                         |

|              | B9  | Data bit          | X                 | X                  |                                                                                                                                                                                                                                         |

|              | B10 | Data bit          | X                 | X                  |                                                                                                                                                                                                                                         |

|              | B11 | Data bit          | X                 | X                  |                                                                                                                                                                                                                                         |

|              | B12 | Data bit          | X                 | X                  |                                                                                                                                                                                                                                         |

|              | B13 | Data bit          | X                 | X                  |                                                                                                                                                                                                                                         |

|              | B14 | Data bit          | X                 | X                  |                                                                                                                                                                                                                                         |

|              | B15 | Data bit          | X                 | X                  |                                                                                                                                                                                                                                         |

|              | B16 | Data bit          | Х                 | X                  |                                                                                                                                                                                                                                         |

| Data field   | B17 | Data bit          | X                 | X                  |                                                                                                                                                                                                                                         |

| Data field   | B19 | Data bit          | X                 | X                  |                                                                                                                                                                                                                                         |

|              | B20 | Data bit          | X                 | X                  |                                                                                                                                                                                                                                         |

|              | B21 | Data bit          | X                 | X                  |                                                                                                                                                                                                                                         |

|              | B22 | Data bit          | Х                 | X                  |                                                                                                                                                                                                                                         |

|              | B23 | Data bit          | X                 | X                  |                                                                                                                                                                                                                                         |

|              | B24 | Data bit          | X                 | X                  |                                                                                                                                                                                                                                         |

|              | B25 | Data bit          | X                 | X                  |                                                                                                                                                                                                                                         |

|              | B26 | Data bit          | X                 | X                  |                                                                                                                                                                                                                                         |

|              | B27 | Data bit          | Х                 | X                  |                                                                                                                                                                                                                                         |

|              | B28 | Data bit          | X                 | X                  |                                                                                                                                                                                                                                         |

|              | B29 | Data bit          | X                 | X                  |                                                                                                                                                                                                                                         |

|              | B30 | Data bit          | X                 | X                  |                                                                                                                                                                                                                                         |

|              | B31 | Data bit<br>(MSB) | Х                 | Х                  |                                                                                                                                                                                                                                         |

Submit Documentation Feedback

Copyright © 2009, Texas Instruments Incorporated

# **TX Synthesizer SPI registers**

## SPI1 Register 1

| Regi  | ister add | ress    | SPI ad     | dress      | TX re                  |       |       |       |                 | eference div | nce divider |        |       |       |       |

|-------|-----------|---------|------------|------------|------------------------|-------|-------|-------|-----------------|--------------|-------------|--------|-------|-------|-------|

| Bit0  | Bit1      | Bit2    | Bit3       | Bit4       | Bit5                   | Bit6  | Bit7  | Bit8  | Bit9            | Bit10        | Bit11       | Bit12  | Bit13 | Bit14 | Bit15 |

| TX re | ference o | divider | REF<br>INV | VCO<br>NEG | TX charge-pump current |       |       |       | TX CP<br>DOUBLE | RSV          | RSB         | CP OFF | CP UP | CP DN |       |

| Bit16 | Bit17     | Bit18   | Bit19      | Bit20      | Bit21                  | Bit22 | Bit23 | Bit24 | Bit25           | Bit26        | Bit27       | Bit28  | Bit29 | Bit30 | Bit31 |

| REGISTER<br>1 | NAME          | POWER-ON<br>VALUE | SUGGESTED<br>VALUE | DESCRIPTION                                                                    |

|---------------|---------------|-------------------|--------------------|--------------------------------------------------------------------------------|

| Bit0          | ADDR_0        | 1                 | 1                  | Register address bits                                                          |

| Bit1          | ADDR_1        | 0                 | 0                  |                                                                                |

| Bit2          | ADDR_2        | 0                 | 0                  |                                                                                |

| Bit3          | ADDR_3        | 1                 | 1                  | SPI address bits                                                               |

| Bit4          | ADDR_4        | 0                 | 0                  |                                                                                |

| Bit5          | TXRDIV_0      | 0                 | App. specific      |                                                                                |

| Bit6          | TXRDIV_1      | 0                 | App. specific      | 14-bit reference divider value                                                 |

| Bit7          | TXRDIV_2      | 0                 | App. specific      | (minimum value Rmin = 1;<br>maximum value Rmax = 16,383)                       |

| Bit8          | TXRDIV_3      | 0                 | App. specific      | - maximum value Kmax = 10,500)                                                 |

| Bit9          | TXRDIV_4      | 0                 | App. specific      |                                                                                |

| Bit10         | TXRDIV_5      | 0                 | App. specific      |                                                                                |

| Bit11         | TXRDIV_6      | 0                 | App. specific      |                                                                                |

| Bit12         | TXRDIV_7      | 0                 | App. specific      |                                                                                |

| Bit13         | TXRDIV_8      | 0                 | App. specific      |                                                                                |

| Bit14         | TXRDIV_9      | 0                 | App. specific      |                                                                                |

| Bit15         | TXRDIV_10     | 0                 | App. specific      |                                                                                |

| Bit16         | TXRDIV_11     | 0                 | App. specific      |                                                                                |

| Bit17         | TXRDIV_12     | 0                 | App. specific      |                                                                                |

| Bit18         | TXRDIV_13     | 0                 | App. specific      |                                                                                |

| Bit19         | TXREF_INV     | 0                 | 0                  | Invert reference-clock polarity; 1 = use falling edge                          |

| Bit20         | TXNEG_VCO     | 1                 | 1                  | VCO polarity control; 1 = negative slope (negative K <sub>v</sub> )            |

| Bit21         | TXICP_0       | 0                 | 0                  | Program charge-pump dc current, I <sub>CP</sub> , from 0.5 mA (1 1111) to 2 mA |

| Bit22         | TXICP_1       | 1                 | 1                  | (0 0000);<br>default value 1 mA (0 1010)                                       |

| Bit23         | TXICP_2       | 0                 | 0                  | default value 1 mix (0 1010)                                                   |

| Bit24         | TXICP_3       | 1                 | 1                  |                                                                                |

| Bit25         | TXICP_4       | 0                 | 0                  |                                                                                |

| Bit26         | TXICPDOUBLE   | 0                 | 0                  | 1 = set I <sub>CP</sub> to double the current                                  |

| Bit27         | RSV           | 0                 | 0                  | Reserved                                                                       |

| Bit28         | RSV           | 0                 | 0                  | Reserved                                                                       |

| Bit29         | TXCP_OVERRIDE | 0                 | 0                  | 1 = disable charge pump                                                        |

| Bit30         | TXCP_UP       | 0                 | 0                  | 1 = enable the charge-pump source current in disable mode                      |

| Bit31         | TXCP_DN       | 0                 | 0                  | 1 = enable the charge-pump sink current in disable mode                        |

Product Folder Link(s): TRF2443

# SPI1 Register 2

| Reg   | ister add | Iress     | SPI ad | ddress | TX N-divider value |                                                          |       |       |       |       |                            |       |       |       |        |

|-------|-----------|-----------|--------|--------|--------------------|----------------------------------------------------------|-------|-------|-------|-------|----------------------------|-------|-------|-------|--------|

| Bit0  | Bit1      | Bit2      | Bit3   | Bit4   | Bit5               | Bit5 Bit6 Bit7 Bit8 Bit9 Bit10 Bit11 Bit12 Bit13 Bit14 B |       |       |       |       |                            | Bit15 |       |       |        |

|       | TX N      | l-divider | value  |        |                    | RSV                                                      |       |       |       |       | DIV 8–16 CAL clock divider |       |       |       | EN CAL |